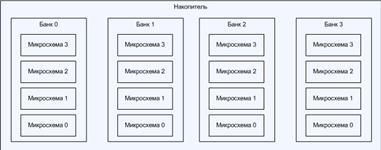

Компоновка банков накопителя

Накопитель организован на 16 микросхемах ФЛЭШ-памяти K9K49G08U0M, которые разделим на четыре банка, по четыре микросхемы в каждом банке (рисунок 3.7). Это сделано для того чтобы иметь возможность устранить времена простоя (занятости) накопителя при циклах записи. Все 16 микросхем имеют общую шину данных, сигналы записи, чтения, записи команд и адреса. Выборка между микросхемами осуществляется сигналом Выбора микросхемы (СЕ). Сигналы R/B (свободен/занят) микросхем, объединенных в банк, соединены, следовательно для анализа контроллеру доступно четыре сигнала свободен/занят (R/B) определяющие занятость банков.

Рисунок 3.7 – Структура накопителя

Такое построение накопителя с одной стороны позволяет производить непрерывную запись в него, а с другой стороны оптимизирует число линий связи необходимое для его обслуживания.