Проектирование интерфейсного модуля

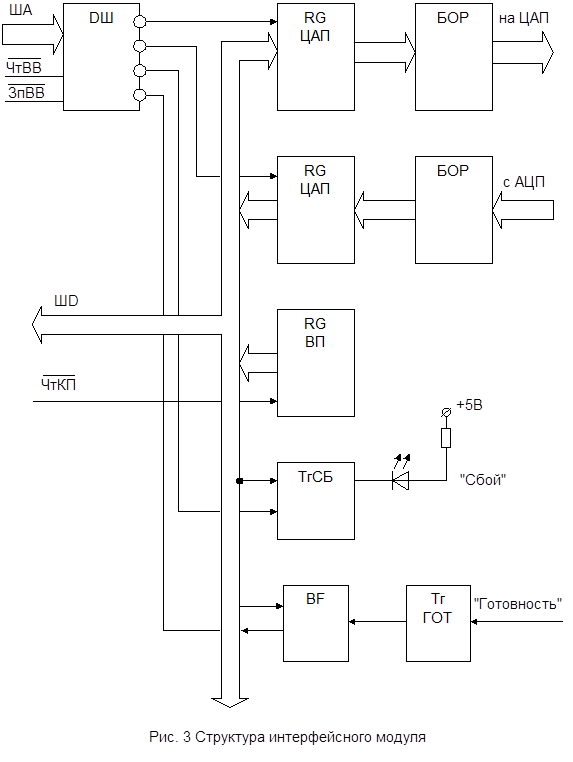

В состав интерфейсного модуля (рис. 3) входят следующие блоки:

адресный дешифратор (ДШ);

регистр цифро-аналогового преобразователя (RG ЦАП);

регистр аналого-цифрового преобразователя (RG АЦП);

регистр вектора прерывания (RG ВП);

триггер "Сбой" (Тг СБ);

триггер "Готовность" (Тг ГОТ);

буфер-формирователь (BF);

блоки оптронной развязки (БОР).

Адресный дешифратор производит выбор порта (регистра или триггера) с которым производится обмен информацией путем дешифрации его адреса, поступившего с ША. По сигналу, поступающему с ДШ, производится либо синхронизация вводимой информации в порт , либо вывод выходов порта из высокоимпедасного состояния при чтении содержимого портов.

Регистр ЦАП служит для хранения цифрового эквивалента управляющего напряжения для его последующего преобразования в аналоговую вели чину в цифро-аналоговом преобразователе.

Регистр АЦП служит для приема и хранения цифрового эквивалента напряжения тахогенератора UТГ, после его преобразования в АЦП.

Регистр вектора прерывания хранит код команды RST. По сигналу "Чтение контроллера прерываний" ![]() выходы регистра выводятся из высокоимпедансного состояния, что обеспечивает выдачу хранимого кода на ШД.

выходы регистра выводятся из высокоимпедансного состояния, что обеспечивает выдачу хранимого кода на ШД.

Информационный вход триггера СБ подключается к одному из разрядов ШД. Синхронизация записи в триггер осуществляется сигналом с ДШ.

Запись информации в триггер ГОТ осуществляется внешними сигналами (информационным и синхронизирующим), поступающими с электропривода. Для того, чтобы не блокировать один из разрядов ШД состоянием триггера (0 или 1) выход триггера подключается к одному из разрядов ШД через буфер-формирователь (ВF), имеющий третье состояние. Вывод буфера из этого со стояния (подключение триггера к ШД) осуществляется сигналом с ДШ.