Выбор элементной базы

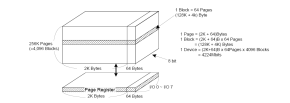

Микросхема K9K4G08U0M – это память объемом 4224 Мбит, организованная как 262144 строки (страницы) по 2112×8 столбцов. Запасные 64 столбца находятся по адресам начатая с 2048 по 2111. 2112-ти байтовый регистр данных и 2112-ти байтовый кэш-регистр последовательно соединен с остальными. Эти последовательно соединенные регистры соединены с массивом ячеек памяти, для согласования передачи данных между I/O буферами и ячейками памяти при операции чтения или записи страницы. Массив памяти складывается из 32-х ячеек, последовательно соединенных для формирования И-НЕ структуры. Каждая из 32 ячеек находятся на различных страницах. Блок состоит из 2 строк с И-НЕ структурой. И-НЕ структура состоит из 32 ячеек. Всего в блоке 1081344 И-НЕ ячеек. Операции чтения и записи выполняются постранично, тогда, как операция стирания выполняется поблочно. Массив памяти состоит из 4096 отдельно стираемых блоков объемом 128 Кбайт. Структура микросхемы K9K4G08U0M приведена на рисунке 2.3.

Рисунок 2.3 – Структура микросхемы K9K4G08U0M

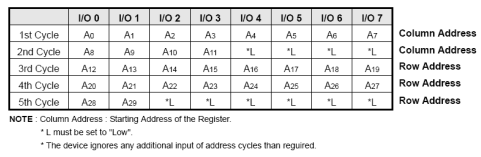

Адрес K9K4G08U0M мультиплексирован на 8 выводов (таблица 2.1). Такая схема существенно уменьшает число выводов и допускает дальнейшее повышение плотности с сохранением согласованности на системной плате. Команды, адрес и данные записываются через входы/выходы переводом WE в низкий уровень при низком уровне на входе СЕ. Данные сохраняются по фронту сигнала WE. Сигналы разрешение записи команды (CLE) и разрешение записи команды адреса (ALE) используются для мультиплексирования команд и адреса соответственно из приходящих на входы/выходы данных. Некоторые команды требуют одного шинного цикла, например, команда сброса, команда чтения состояния и т.д. Для других команд, таких как чтение страницы, стирание блока и запись страницы, необходимо 2 цикла: один на установку и другой – на исполнение команды. 512 Мбайт физического объема требуют 30-разрядного адреса, таким образом, необходимо 5 циклов записи адреса: 2 цикла для адресации по столбцам (Column) и 3 цикла для адресации по строкам (Row).

Таблица 2.1 – Адресация микросхемы K9K4G08U0M

Для операции чтения и записи страницы так же необходимы 5 циклов записи адреса, следующие за нужной командой. Однако для операции стирания блока требуется всего 3 цикла записи адреса (адрес страницы). Операции с устройством выбираются записью специальных команд в командный регистр (таблица 2.2).

Таблица 2.2 – Список команд микросхемы K9K4G08U0M

|

Функция |

1 цикл |

2 цикл |

Внеочередная команда |

|

Чтение |

00h |

30h | |

|

Чтение для перезаписи |

00h |

35h | |

|

Чтение сигнатуры |

90h |

- | |

|

Сброс |

FFh |

- |

V |

|

Запись на страницу |

80h |

10h | |

|

Запись в кэш |

80h |

15h | |

|

Перезапись |

85h |

10h | |

|

Стирание блока |

60h |

D0h | |

|

Произвольный ввод данных* |

85h |

- | |

|

Произвольный вывод данных* |

05h |

E0h | |

|

Чтение статуса |

70h |

- |

V |